错误处理方法、处理系统及计算设备与流程

本申请涉及,具体涉及一种错误处理方法、处理系统及计算设备。

背景技术:

1、随着计算技术的发展,片上系统(system-on-a-chip,soc)在各个领域均得到广泛的应用。在片上系统的运行过程中,可能会因为各种原因导致出现错误,从而导致片上系统的工作出现异常,甚至宕机。为了监测上述错误并进行相应的处理,相关技术中提出了基于可靠可用性服务(reliability availability serviceability,ras)机制进行错误处理的方法。然而,相关技术中的基于ras的错误处理方法的性能有待于进一步地提高。

技术实现思路

1、本申请提供一种错误处理方法、处理系统及计算设备,下面对本申请实施例涉及的各个方面进行介绍。

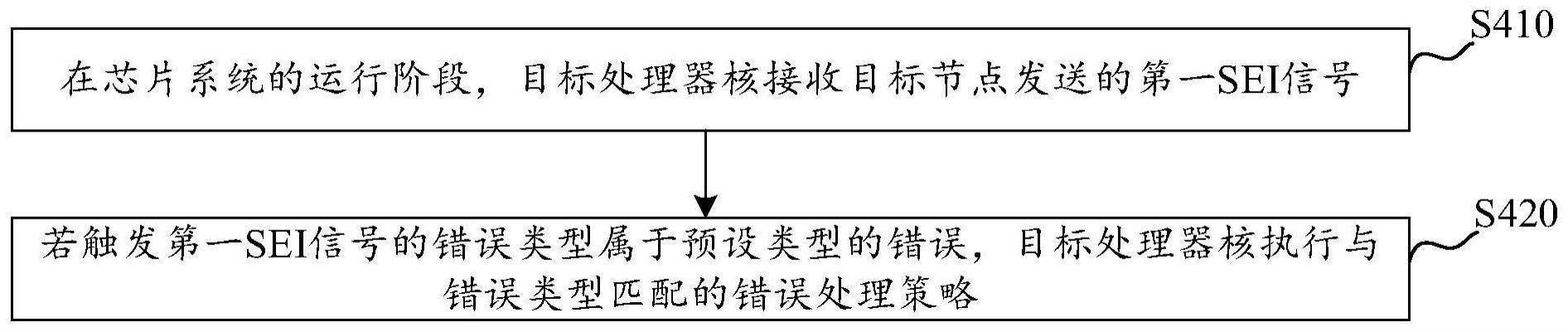

2、第一方面,提供了一种错误处理方法,所述方法应用于片上系统,所述片上系统包括至少一个处理器核和目标节点,所述至少一个处理器核包括目标处理器核,所述方法包括:在芯片系统的运行阶段,所述目标处理器核接收所述目标节点发送的第一sei信号;若触发所述第一使能中断(set interrupt enable,sei)信号的错误类型属于预设类型的错误,所述目标处理器核执行与所述错误类型匹配的错误处理策略,其中,所述预设类型的错误包括处理器核的错误和/或中断控制器的错误。

3、在本申请实施例中,当片上系统发生异常时会触发第一sei信号,相应地,当目标处理器核接收到第一sei信号时,若触发第一sei信号的错误属于的预设类型的错误,则目标处理器核可以执行与错误类型匹配的错误处理策略,相比于传统方案中基于ras的错误处理方法,有助于提高错误处理的性能。

4、另一方面,sei信号是arm芯片架构内的系统错误中断信号,与中断请求的中断信号不同,sei信号可以不依靠处理器核外的中断管理控制器,当处理器核上电后就可以工作,因此,在本申请实施例中,若发生系统错误来触发不依赖于中断控制器的第一sei信号,有助于及时发现中断控制器的错误。

5、在一些实现方式中,若所述处理器核的错误为所述至少一个处理器核中一个处理器核产生的错误,所述错误处理策略与产生错误的处理器核的类型关联,所述处理器核的类型包括主核或从核,其中,所述主核用于为所述从核调度所述片上系统中的资源。

6、在本申请实施例中,错误处理策略与产生错误的处理器核的类型关联,有助于提高设置错误处理策略的合理性。

7、在一些实现方式中,若所述产生错误的处理器核的类型为主核,则与所述错误类型匹配的错误处理策略包括对所述芯片系统进行复位。

8、在本申请实施例中,若产生错误的处理器核的类型为主核,则与错误类型匹配的错误处理策略包括对芯片系统进行复位,有助于提高主核正常运行的可能性,以确保片上系统的性能。

9、在一些实现方式中,若所述产生错误的处理器核的类型为从核,则与所述错误类型匹配的错误处理策略包括对所述目标处理器核进行单核复位。

10、在本申请实施例中,若产生错误的处理器核的类型为从核,则与错误类型匹配的错误处理策略包括目标处理器核进行单核复位,有助于提高主核正常运行的可能性,以确保片上系统的性能。

11、在一些实现方式中,所述至少一个处理器核中的部分或全部处理器核属于目标核簇,若所述处理器核错误包括所述目标核簇产生的错误,所述错误处理策略与所述目标核簇的类型关联,所述目标核簇的类型包括主核簇或辅助核簇。

12、在本申请实施例中,错误处理策略与目标核簇的类型关联,有助于提高设置错误处理策略的合理性。

13、在一些实现方式中,若所述目标核簇为主核簇,则与所述错误类型匹配的错误处理策略包括对所述芯片系统执行复位操作。

14、在本申请实施例中,若目标核簇为主核簇,则与错误类型匹配的错误处理策略包括对芯片系统进行复位,有助于提高主核簇正常运行的可能性,以确保片上系统的性能。

15、在一些实现方式中,若所述目标核簇为辅助核簇,则与所述错误类型匹配的错误处理策略与所述目标核簇中除第一处理器核之外的剩余处理器核的运行状态关联,所述第一处理器核为发现所述当前错误的处理器核。

16、在本申请实施例中,若目标核簇为辅助核簇,则基于剩余处理器核的运行状态来设置匹配的错误处理策略,有助于减少发生错误的处理核对其他处理器核的影响的同时,提高辅助核簇正常工作的可能性。

17、在一些实现方式中,若所述剩余处理器核包括处于运行状态的处理器核,则与所述错误类型匹配的错误处理策略包括控制所述第一处理器核进入休眠状态。

18、在一些实现方式中,若所述剩余处理器核均处于休眠状态,则与所述错误类型匹配的错误处理策略包括对所述目标核簇进行复位。

19、在本申请实施例中,若剩余处理器核包括处于运行状态的处理器核,则控制第一处理器核进入休眠状态,以减少其他模型对第一处理器核的访问,有助于提高片上系统正常工作的可能性。

20、在一些实现方式中,如果所述当前错误属于中断控制器的错误,则与所述错误类型匹配的错误处理策略包括复位所述中断控制器。

21、在本申请实施例中,若当前错误属于中断控制器的错误,则与错误类型匹配的错误处理策略包括复位所述中断控制器,有助于提高中断控制器正常工作的可能性。

22、在一些实现方式中,所述方法还包括:在所述芯片系统的启动阶段,所述目标处理器核接收第二sei信号;响应于所述第二sei信号,所述目标处理器核利用电源模块进行复位。

23、在本申请实施例中,在芯片系统的启动阶段,若目标处理器核接收第二sei信号,则目标处理器核利用电源模块进行复位,有助于降低错误处理的复杂度,以提高片上系统正常工作的可能性。

24、在一些实现方式中,所述方法还包括:响应于所述第一sei信号,所述目标处理器核保护现场;如果所述当前错误不属于预设类型的错误,则所述目标处理器核恢复现场。

25、在本申请实施例中,若接收到第一sei信号,则目标处理器核可以保护现场,并在当前错误不属于预设类型的错误,则恢复现场,有助于提高片上系统运行的连续性。

26、第二方面,提供了一种处理系统,包括:存储器,用于存储程序;处理器核,用于执行所述程序,以执行第一方面中所述的方法。

27、第三方面,提供了一种计算设备,包括如第二方面所述的处理系统。

28、第四方面,提供了一种计算机可读介质,所述计算机可读介质存储有程序代码,当所述计算机程序代码在计算机上运行时,使得计算机执行上述第一方面中所述的方法。

29、第五方面,提供了一种计算机程序产品,所述计算机程序产品包括计算机程序/指令,当所述计算机程序/指令处理器被执行时实现如第一方面中所述的方法。

30、在一些实现方式中,上述计算机程序产品包括可以包括计算机程序代码,当计算机程序代码在计算机上运行时,使得计算机执行上述第一方面中所述的方法。

技术特征:

1.一种错误处理方法,其特征在于,所述方法应用于片上系统,所述片上系统包括至少一个处理器核和目标节点,所述至少一个处理器核包括目标处理器核,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,若所述处理器核的错误为所述至少一个处理器核中一个处理器核产生的错误,所述错误处理策略与产生错误的处理器核的类型关联,所述处理器核的类型包括主核或从核,其中,所述主核用于为所述从核调度所述片上系统中的资源。

3.根据权利要求2所述的方法,其特征在于,若所述产生错误的处理器核的类型为主核,则与所述错误类型匹配的错误处理策略包括对所述芯片系统进行复位。

4.根据权利要求2所述的方法,其特征在于,若所述产生错误的处理器核的类型为从核,则与所述错误类型匹配的错误处理策略包括对所述目标处理器核进行单核复位。

5.根据权利要求1所述的方法,其特征在于,所述至少一个处理器核中的部分或全部处理器核属于目标核簇,若所述处理器核的错误包括所述目标核簇产生的错误,所述错误处理策略与所述目标核簇的类型关联,所述目标核簇的类型包括主核簇或辅助核簇。

6.根据权利要求5所述的方法,其特征在于,若所述目标核簇为主核簇,则与所述错误类型匹配的错误处理策略包括对所述芯片系统执行复位操作。

7.根据权利要求5所述的方法,其特征在于,若所述目标核簇为辅助核簇,则与所述错误类型匹配的错误处理策略与所述目标核簇中除第一处理器核之外的剩余处理器核的运行状态关联,所述第一处理器核为发现当前错误的处理器核。

8.根据权利要求7所述的方法,其特征在于,若所述剩余处理器核包括处于运行状态的处理器核,则与所述错误类型匹配的错误处理策略包括控制所述第一处理器核进入休眠状态。

9.根据权利要求7所述的方法,其特征在于,若所述剩余处理器核均处于休眠状态,则与所述错误类型匹配的错误处理策略包括对所述目标核簇进行复位。

10.根据权利要求1所述的方法,其特征在于,如果所述当前错误属于中断控制器的错误,则与所述错误类型匹配的错误处理策略包括复位所述中断控制器。

11.根据权利要求1所述的方法,其特征在于,所述方法还包括:

12.根据权利要求1所述的方法,其特征在于,所述方法还包括:

13.一种处理系统,其特征在于,包括:

14.一种计算设备,其特征在于,包括如权利要求13所述的处理系统。

15.一种计算机可读存储介质,其特征在于,其上存储有用于执行如权利要求1至12中任一项所述的方法的程序。

技术总结

本申请提供了一种错误处理方法、处理系统及计算设备,方法应用于片上系统,片上系统包括至少一个处理器核和目标节点,至少一个处理器核包括目标处理器核,方法包括:在芯片系统的运行阶段,目标处理器核接收目标节点发送的第一SEI信号;若触发第一SEI信号的错误类型属于预设类型的错误,目标处理器核执行与错误类型匹配的错误处理策略,其中,预设类型的错误包括处理器核的错误和/或中断控制器的错误。在本申请实施例中,当目标处理器核接收到第一SEI信号时,若触发第一SEI信号的错误属于的预设类型的错误,相应地目标处理器核可以执行与错误类型匹配的错误处理策略,相比于基于RAS的错误处理方法,有助于提高错误处理的性能。

技术研发人员:彭崇武,刘勇鹏,王银峰,王旭

受保护的技术使用者:飞腾信息技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!